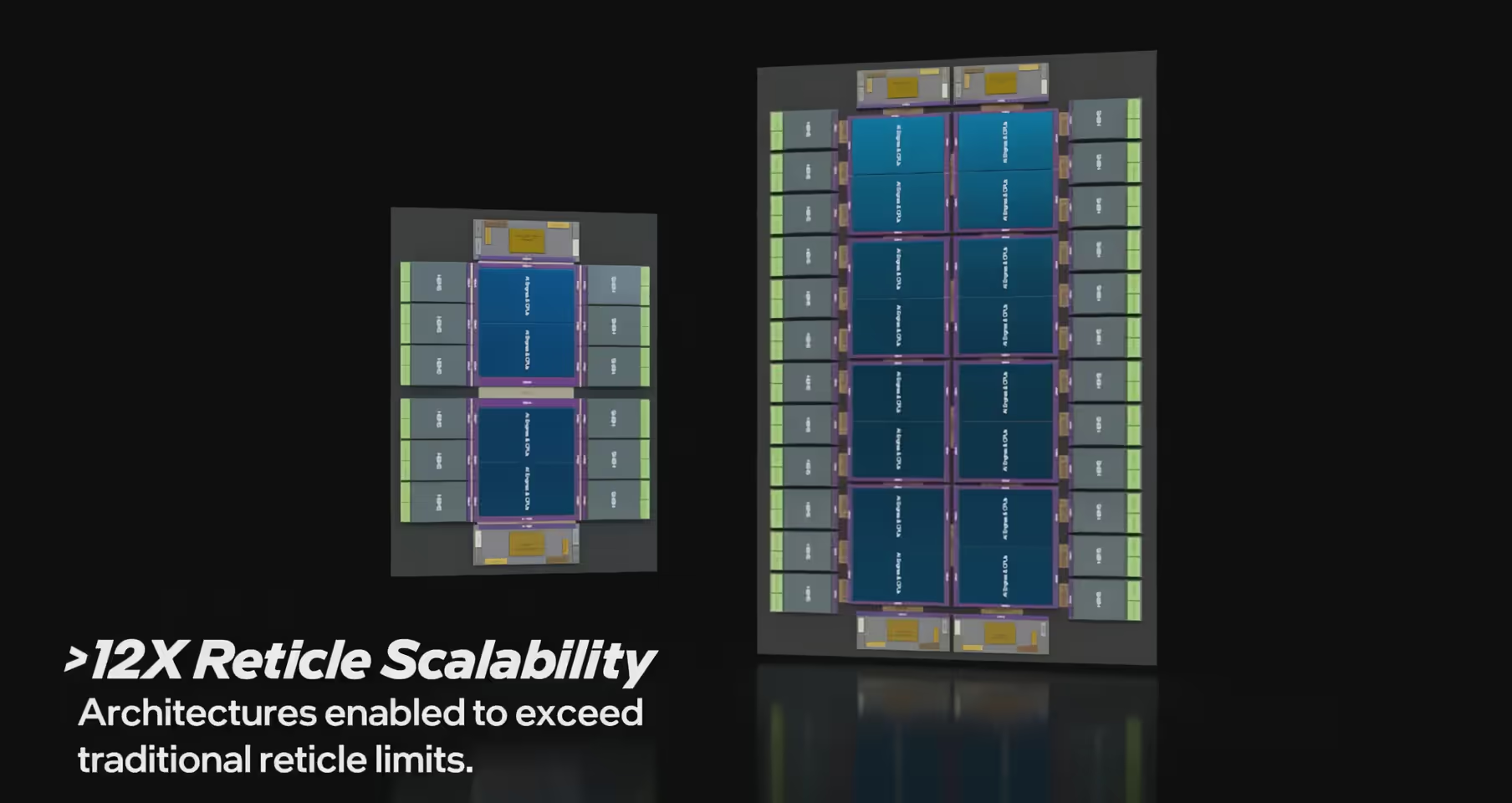

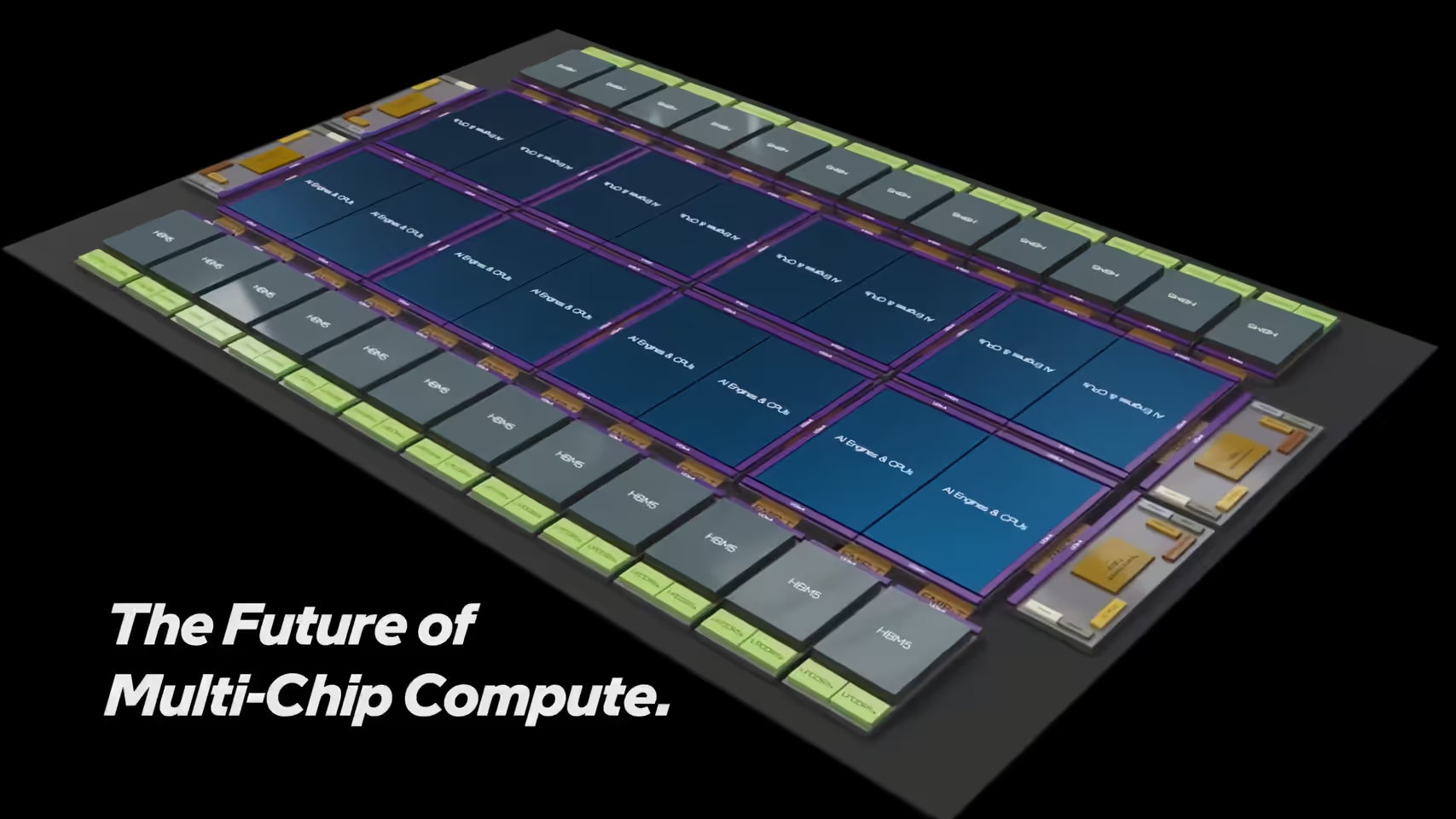

Intel Foveros 3D et EMIB-T : jusqu’à 16 dies et 24 HBM5 dans un seul package

Intel Foveros s’attaque au mur du réticule : Intel affiche un package 12 fois plus grand que les 830 mm², capable de réunir 16 compute dies et 24 modules HBM5. Selon une courte démonstration de sa division Foundry, le groupe agrège ses interconnexions Foveros 3D et EMIB-T et s’appuie sur ses nœuds 18A et 14A pour franchir l’échelle classique des monolithes.

Intel Foveros 3D et EMIB-T : 16 dies, 24 HBM5, 12× la taille de réticule

Le schéma retenu superpose des base dies en 18A-PT, dotés d’un backside power delivery pour doper la densité logique et la fiabilité. Ces dies de base intègrent des structures SRAM proches de l’architecture Clearwater Forest et servent de socle à des tuiles de calcul gravées en 14A/14A-E, qui combinent transistors RibbonFET de seconde génération et PowerDirect.

La liaison verticale s’effectue via Foveros Direct 3D et son hybrid bonding à pas ultrafin, tandis que EMIB-T ajoute des TSV pour des liens chiplet à très large bande passante. D’après Intel, l’ensemble supporte toutes les normes HBM, dont HBM4, HBM5 et leurs successeurs.

Nœuds 18A, 18A-P/18A-PT et 14A : cap sur la production et des clients externes

Intel aligne ses procédés 18A, y compris 18A-P et 18A-PT, ainsi que 14A pour la production de masse et l’accueil de clients tiers. La firme évoque des packages semblables à ceux de l’ex-Ponte Vecchio pour ses accélérateurs « Jaguar Shores ». À mesure que ses capacités de packaging s’étendent, il semblerait que des partenaires voient en Intel un concurrent sérieux des CoWoS de TSMC. Dans la vidéo, Intel résume l’ambition : « 12× la taille de réticule, 16 compute dies et 24 HBM5 ».

La feuille de route ne s’arrête pas là. Intel vise, avec Foveros-B et des régulateurs de tension intégrés (IVR), des GPU à 5 000 W d’ici 2027. Un design extrême, mais cohérent avec la montée en puissance des accélérateurs IA et la densification des interconnexions.

Source : TechPowerUp